# Size Oblivious Programming with *InfiniMem*\*

Sai Charan Koduru, Rajiv Gupta, Iulian Neamtiu

Department of Computer Science and Engineering University of California, Riverside {scharan,gupta,neamtiu}@cs.ucr.edu

**Abstract.** Many recently proposed BigData processing frameworks make programming easier, but typically expect the datasets to fit in the memory of either a single multicore machine or a cluster of multicore machines. When this assumption does not hold, these frameworks fail. We introduce the InfiniMem framework that enables size oblivious processing of large collections of objects that do not fit in memory by making them disk-resident. InfiniMem is easy to program with: the user just indicates the large collections of objects that are to be made disk-resident, while InfiniMem transparently handles their I/O management. The InfiniMem library can manage a very large number of objects in a uniform manner, even though the objects have different characteristics and relationships which, when processed, give rise to a wide range of access patterns requiring different organizations of data on the disk. We demonstrate the ease of programming and versatility of *InfiniMem* with 3 different probabilistic analytics algorithms, 3 different graph processing size oblivious frameworks; they require minimal effort, 6–9 additional lines of code. We show that InfiniMem can successfully generate a mesh with 7.5 million nodes and 300 million edges (4.5 GB on disk) in 40 minutes and it performs the PageRank computation on a 14GB graph with 134 million vertices and 805 million edges at 14 minutes per iteration on an 8-core machine with 8 GB RAM. Many graph generators and processing frameworks cannot handle such large graphs. We also exploit InfiniMem on a cluster to scale-up an object-based DSM.

#### 1 Introduction

BigData processing frameworks are an important part of today's data science research and development. Much research has been devoted to scale-out performance via distributed processing [8,12,13,17] and some recent research explores scale-up [1,6,11,15,16,21]. However, these scale-up solutions typically assume that the input dataset fits in memory. When this assumption does not hold, they simply fail. For example, experiments by Bu et al. [4] show that different open-source Big Data computing systems like Giraph [1], Spark [21], and Mahout [19] often crash on various input graphs. Particularly, in one of the experiments, a 70GB web graph dataset was partitioned across 180 machines (each with 16 GB RAM) to perform the PageRank computation. However, all the systems crashed with java.lang.OutOfMemoryError, even though there was less

$<sup>^\</sup>star$  This work was supported by NSF Grant CCF-1524852, CCF-1318103, CNS-1157377, CCF-0963996, CCF-0905509, and a Google Research Award.

than 500MB of data to be processed per machine. In our experiments we also found that GTgraph's popular R-MAT generator [2], a tool commonly used to generate power-law graphs, crashed immediately with a *Segmentation Fault* from memory allocation failure when we tried to generate a graph with 1M vertices and 400M edges on a machine with 8GB RAM.

Motivated by the above observations, in this paper, we develop *InfiniMem*, a system that enables Size Oblivious Programming - the programmer develops the applications without concern for the input sizes involved and InfiniMem ensures that these applications do not run out of memory. Specifically, the InfiniMem library provides interfaces for transparently managing a large number of objects stored in files on disk. For efficiency, InfiniMem implements different read and write policies to handle objects that have different characteristics (fixed size vs. variable size) and require different handling strategies (sequential vs. random access I/O). We demonstrate the ease of programming with Infin*iMem* by programming BigData analysis applications like frequency estimation, exact membership query, and Bloom filters. We further demonstrate the versatility of InfiniMem by developing size oblivious graph processing frameworks with three different graph data representations: vertex data and edges in a single data structure; decoupled vertex data and edges; and the shard representation used by GraphChi [11]. One advantage of InfiniMem is that it allows researchers and programmers to easily experiment with different data representations with minimal additional programming effort. We evaluate various graph applications with three different representations. For example, a quick and simple shard implementation of PageRank with InfiniMem performs within  $\sim 30\%$  of GraphChi.

The remainder of the paper is organized as follows: Section 2 motivates the problem and presents the requirements expected from a *size oblivious programming* system. Section 3 introduces the programming interface for size oblivious programming. Section 4 describes the object representation used by *InfiniMem* in detail. Section 5 describes the experimental setup and results of our evaluation. Related work and conclusions are presented in Sections 6 and 7, respectively.

# 2 Size Oblivious Programming

The need to program processing of very large data sets is fairly common today. Typically a processing task involves representing the data set as a large collection of objects and then performing analysis on them. When this large collection of objects does not fit in memory, the programmer must spend considerable effort on writing code to make use of disk storage to manage the large number of objects. In this work we free the programmer from this burden by developing a system that allows the programmer to write size oblivious programs, i.e., programs where the user need not explicitly deal with the complexity of using disk storage to manage large collections of objects that cannot be held in available memory. To enable the successful execution of size oblivious programs, we propose a general-purpose programming interface along with an I/O efficient representation of objects on disk. We now introduce a few motivating applications and identify requirements to achieve I/O efficiency for our size oblivious programming system.

**Motivating applications:** Consider an application that is reading continuously streaming input into a Hash Table in heap memory (lines 1–3, Algorithm 1); a website analytics data stream is an excellent example of this scenario. When the memory gets full, the insert on line 3 could fail, resulting in an application failure. Similarly, consider the GTGraph [2] graph generator which fails to generate a graph with 1M edges and 400M vertices. Consider a common approach to graph generation which assumes that the entire graph can be held in memory during generation, as illustrated by lines 8-15 in Algorithm 1. First, memory for NUM-VERTICES is allocated (line 8) and then the undirected edges are generated (lines 11-13). Note that the program can crash as early as line 8 when memory allocation fails due to a large number of vertices. Finally, consider the problem of graph processing, using SSSP as a proxy for a large class of graph processing applications. Typically, such applications have three phases: (1) input, (2) compute, and (3) output. The pseudocode for SSSP is outlined in lines 16–31 in Algorithm 1, highlighting these three phases. Note that if the input graph does not fit in memory, this program will not even begin execution.

**Algorithm 1:** Motivating applications: Membership Query, Mesh Generation and Graph Processing.

```

1 HashTable ht;

16 Graph g;

17

while not end of input file do

while read(value) do

read next:

18

ht.insert(value);

g.Add( \alpha(\text{next}) );

19

while more items do

4

repeat

20

if ht.find(item) then

5

termCondition \leftarrow true;

21

print("Item found");

forall the Vertices v in g do

22

for int i=0; i < v.nbrs(); i++ do

23

Vertex n = v.neighbors[i]:

24

Mesh m(NUM-VERTICES)

8

25

if v.dst > n.dst + v.wt/i then

9 foreach node n in Mesh m do

v.dst \leftarrow (n.dst + v.wt[i]);

26

\leftarrow \text{rand}(0, \text{MAX});

10

for j=0; j < i; j++ do | n.addNeighbor(m[j]);

11

if NOT converged then

27

12

termCondition \leftarrow false;

28

m[j].addNeighbor(n);

13

until termCondition is true:

29

14 foreach Node \ n \ in \ Mesh \ m \ do

foreach Node n in Graph g do

Write(n)

15

Write(n);

```

Our solution: We focus on supporting size oblivious programming for C++ programs via the InfiniMem C++ library and runtime. Examples in Algorithm 1 indicate that the data structures that can grow very large are represented as collections of objects. Size Oblivious Programming with InfiniMem simply requires programmers to identify potentially large collections of objects using very simple abstractions provided by the library and these collections are transparently made disk-resident and can be efficiently and concurrent accessed. We now analyze these representative applications to tease out the requirements for size oblivious programming that have influenced the architecture of InfiniMem.

Let us reconsider the pseudocode in Algorithm 1, mindful of the requirement of efficient I/O. Lines 5–6 will execute for *every* key in the input; similarly, lines 9 and 14 indicate that lines 10–13 and line 15 will be executed for *every* node in the mesh. Similarly, line 22 indicates that lines 23–26 will be performed on *every*

vertex in the graph. It is natural to read a contiguous block of data so that no additional I/O is required for lines 24–26 for the vertices and is an efficient disk I/O property. Moreover, this would be useful for any application in general, by way of decreasing I/O requests and batching as much I/O as possible. Therefore, we have our first requirement:

#### Support for efficient block-based IO.

Consider next, the example of the hash table where the input data is *not* sorted; then, line 3 of Algorithm 1 motivates need for random access for indexing into the hash table. As another example, observe that line 24 in Algorithm 1 fetches every neighbor of the current vertex. When part of this graph is diskresident, we need a way of efficiently fetching the neighbors, much like *random access* in memory. This is important because any vertex in a graph serves two roles: (1) vertex and (2) neighbor. For the role (1), if vertices are contiguously stored on disk block-based I/O can be used. However, when the vertex is accessed as a neighbor, the neighbor could be stored anywhere on disk, and thus requires an imitation of random access on the disk. Hence our next requirement is:

#### Support for efficient, random access to data on disk.

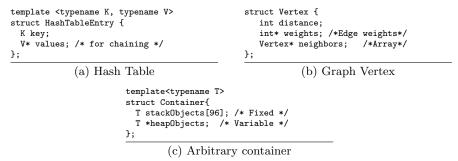

To make the case for our final requirement, consider a typical definition of the HashTable shown in Figure 1a. Each key can store multiple values to support chaining. Clearly, each HashTableEntry is a variable sized entity, as it can hold multiple values by chaining. As another example, consider the definition for a Vertex shown in Figure 1b: the size of neighbors array can vary; and with the exception of the neighbors member, the size of a Vertex can be viewed as a fixed-size object. When reading/writing data from/to the disk, one can devise very fast block-based I/O for fixed-size data (Section 4). However, reading variable-sized data requires remembering the size of the data and performing n reads of appropriate sizes; this is particularly wasteful in terms of disk I/O bandwidth utilization. For example, if the average number of neighbors is 10, every time a distance value is needed, we will incur a 10x overhead in read but useless data. As a final example, Figure 1c is an example of an arbitrary container that showcases the need for both fixed and variable sized data. Hence we arrive at our final requirement from InfiniMem:

# Support to speed up I/O for variable-sized data.

Fig. 1: Common data structure declarations to motivate the need for explicit support for fixed and variable sized data, block based and random IO.

The goal of *InfiniMem* is to transparently support disk-resident versions of object collections so that they can grow to large sizes without causing programs to crash. *InfiniMem*'s design allows size oblivious programming with little effort as the programmer merely identifies the presence and processing of potentially large object collections via *InfiniMem*'s simple programming interface. The details of how *InfiniMem* manages I/O (i.e., uses block-based I/O, random access I/O, and I/O for fixed and variable sized data) during processing of a disk-resident data structure are hidden from the programmer.

# 3 The *InfiniMem* Programming Interface

InfiniMem is a C++ template library that allows programmers to identify size oblivious versions of fixed- and variable-sized data collections and enables transparent, efficient processing of these collections. We now describe InfiniMem's simple application programming interface (API) that powers size oblivious programming. InfiniMem provides a high-level API with a default processing strategy that hides I/O details from the programmer; however the programmer has the flexibility to use the low-level API to implement any customized processing.

```

template<typename T>

template<typename T>

T Box::fetch(ID):

struct Container: public Box<T> { // or Bag<T>

T data;

template<tvpename T>

void update() { /* for each T */

T* Box::fetchBatch(ID, count):

template<typename T>

void Box::store(ID, const T*):

void process();

template<typename T>

void Box::storeBatch(ID, count);

typedef Container<int> intData;

template<typename T>

typedef Container<MvObject> objData:

T Bag::fetch(ID);

int main() {

template<typename T>

Infinimem<intData> idata:

T* Bag::fetchBatch(ID, count);

idata.read("/input/file");

idata.process();

template<typename T>

void Bag::store(ID, const T*);

Infinimem<obiData> odata:

odata.read("/input/data/");

template<typename T>

odata.process();

void Bag::storeBatch(ID, count);

}

```

Fig. 2: Programming with *InfiniMem*: the Box and Bag interfaces are used for *fixed size* and *variable sized* objects; process drives the computation using the user-defined update() methods and the low-level fetch() and store() API.

Identifying Large Collection of Objects: In InfiniMem, the programmer identifies object collections that potentially grow large and need to be made disk-resident. In addition, the programmer classifies them as fixed or variable sized. This is achieved by using the Box and Bag abstractions respectively. The Box abstraction can be used to hold fixed-size data, while the Bag holds flexible-sized data. Figure 2 illustrates an example and lists the interface. The programmer uses the Box or Bag interface by simply inheriting from the Box (or Bag) type and provides an implementation for the update() method to process each object in the container. Here, Container is the collection that can potentially grow large,

as identified by the programmer. Infinimem is the default processing engine; *InfiniMem*'s process() function hides the details of I/O and fetches objects as needed by the update() method, thereby enabling *size oblivious programming*.

**Processing Data:** The process() method is the execution engine: it implements the low-level details of efficiently fetching objects from the disk, applies the user-defined update() method and efficiently spills the updated objects to disk. Figure 3 details the default process(). By default, the process()-ing engine fetches, processes and store-es data in batches of size BATCH\_SIZE which is automatically determined from available free memory such that the entire batch fits and can be processed in memory.

While InfiniMem provides the default implementation for process() shown in Figure 3, this method can be overridden: programmers can use the accessors and mutators exposed by InfiniMem (Figure 2) to write their own processing frameworks. Notice that In-

```

// SZ = SIZEOF_INPUT; BSZ = BATCH_SIZE;

Box<T>::process() { // or Bag<T>

for(i=0; i<SZ; i+=BSZ) {

// fetch a portion of Box<T> or Bag<T>

cache = fetchBatch(ID(i), BSZ);

for(j=0; j<BSZ; j++)

cache[j].update();

}

}</pre>

```

frameworks. Notice that *In*- Fig. 3: *InfiniMem*'s generic batch process()-ing. *finiMem* natively supports both sequential/block-based and random accessors and mutators, satisfying each of the requirements formulated earlier. For block-based and random access, *InfiniMem* provides the following intuitively named fetch and store APIs: fetch(), fetchBatch(), store() and storeBatch().

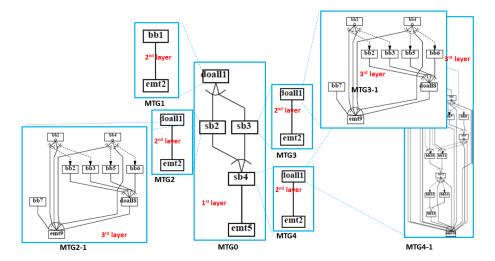

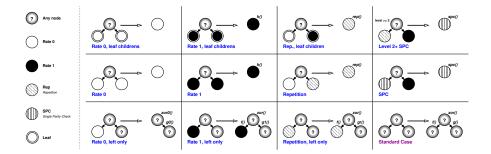

Illustration of InfiniMem for graph processing: We next demonstrate InfiniMem's versatility and ease of use by programming graph applications using three different graph representations. We start with the standard declaration of a Vertex as seen in Figure 1b. An alternate definition of Vertex separates the fixed sized data from variable sized edgelist for IO efficiency, and used in many vertex centric frameworks [12,11]. Finally, we program GraphChi's [11] shards.

Figure 4a declares the Graph to be a Bag of vertices, using the declaration from Figure 1b. With this declaration, the programmer has identified that the collection of vertices is the potentially large collection that can benefit from size oblivious programming. The preprocess() phase partitions the input graph into disjoint intervals of vertices to allow for parallel processing. These examples use a vertex-centric graph processing approach where the update() method of Vertex defines the algorithm to process each vertex in the graph. The process() method of Graph uses the accessors and mutators from Figure 2 to provide a size oblivious programming experience to the programmer. Figure 4b declares a Graph as the composition of a Box of Vertex and a Bag of EdgeLists, where EdgeList is an implicitly defined list of neighbors. Finally, Figure 4c uses a similar graph declaration, with the simple tweak of creating an array of N shard partitions; a shard imposes additional constraints on the vertices that are in the shard: vertices are partitioned into intervals such that all vertices with neighbors in a given vertex interval are all available in the same shard [11], enabling fewer

random accesses by having all vertices' neighbors available before processing each shard. Note that representing shards in *InfiniMem* is very simple.

```

void Vertex::update() {

void Vertex::update() {

void Vertex::update() {

foreach(neighbor n)

foreach(neighbor n)

foreach(neighbor n)

distance = f(n.distance);

distance = f(n.distance);

distance = f(n.distance);

template <typnam V,typnam E> template <typename V,typename E>

template <typename V>

class Graph {

class Graph {

class Graph {

Bag<V> vertices;

Box<V> vertices;

Box<V> vertexShard[N];

Bag<E> edgeLists;

Bag<E> edgeShard[N];

public:

void processShard(int);

void process();

void process();

int main() {

int main() {

int main() {

Graph<Vertex, EdgeList> g;

Graph<Vertex> g;

Graph<Vertex, EdgeList> g;

g.read("/path/to/graph");

g.read("/path/to/graph");

g.read("/path/to/graph");

g.preprocess(); //Partition g.preprocess(); //Partition

g.createShards(N);//Preprocess

g.process();

g.process();

for(int i=0; i<N; i++)</pre>

g.processShard(i);

```

(a) Graph for Vertex in Fig- (b) Decoupling Vertices (c) Using Shard representature 1b. from Edgelists. tion of graphs.

Fig. 4: Variations of graph programming, showcasing the ease and versatility of programming with *InfiniMem*, using its high-level API.

```

// SZ = SIZEOF_INPUT;

// SZ = SIZEOF_INPUT;

// NS = NUM_SHARDS;

// BSZ = BATCH_SIZE;

// BSZ = BATCH_SIZE;

// SS = SIZEOF_SHARD;

// vb = vertices;

// v = vertices;

// vs = vertexShard;

// e = edgeLists;

Graph<V>::process() {

Graph<V, E>::process() {

Graph<V, E>::process() {

for(i=0; i<SZ; i+=BSZ) {</pre>

for(i=0; i<SZ; i+=BSZ) {

for(i=0; i<NS; i++) {

// fetch a batch

// fetch a batch

// fetch entire memory shard

vb=fetchBatch(ID(i), BSZ);

vb=v.fetchBatch(ID(i), BSZ);

mshrd = vs[i].fetchBatch(..,SS);

// fetch corr. edgelist

// fetch sliding shards

eb=e.fetchBatch(ID(i), BSZ);

for(j=0; j<NS; j++)

sshrd += vs[j].fetchBatch(.,.);

sg = buildSubGraph(mshrd,sshrd);

for(j=0; j<BSZ; j++)</pre>

for(j=0; j<BSZ; j++)</pre>

foreach(v in sg)

vb[j].update();

vb[j].update(eb[j]);

v.update();

storeBatch(vb, BSZ);

storeBatch(vb, BSZ);

storeBatch(mshrd, SS);

```

(a) process()-ing graph (b) process() for decou-(c) Custom process() for in Figure 1b. pled Vertex. shards.

Fig. 5: Default and custom overrides for process() via low-level InfiniMem API.

Figure 5a illustrates the default process(): objects in the Box or Bag are read in batches and processed one at a time. For graphs with vertices decoupled from edgelists, vertices and edgelists are read in batches and processed one vertex at a time (Figure 5b); batches are concurrently processed. Figure 5c illustrates

custom shard processing: each memory shard and corresponding sliding shards build the subgraph in memory; then each vertex in the subgraph is processed [11].

# 4 InfiniMem's I/O Efficient Object Representation

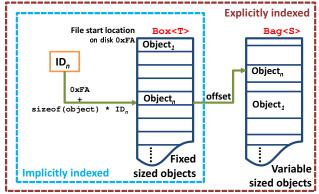

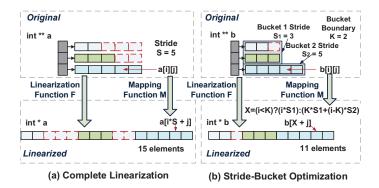

We now discuss the I/O efficient representation provided by *InfiniMem*. Specifically, we propose an *Implicitly Indexed* representation for fixed-sized data (Box); and an *Explicitly Indexed* representation for variable-sized data (Bag).

As the number of objects grows beyond what can be accommodated in main memory, the frequency of object I/O to/from disk storage will increase. This warrants an organization of the disk storage that reduces I/O latency. To allow an object to be addressed regardless of where it resides, it is assigned a unique numeric ID

Fig. 6: Indexed disk representation of fixed- and variable-sized objects.

from a stream of non-negative, monotonically increasing integers. Figure 6 shows the access mechanism for objects using their IDs: fixed-sized data is stored at a location determined by its ID and its fixed size: FILE\_START + (sizeof(Object)\*ID). For variable-sized data, we use a metafile whose fixed-sized address entries store the offset of the variable-sized data into the datafile. The Vertex declared in Figure 4a for example, would only use the explicitly indexed Bag notation to store data, while the representations in Figure 4b and Figure 4c use both the Box and Bag for the fixed size Vertex and the variable sized EdgeList respectively. Thus, fixed-sized data can be fetched/stored in a single logical disk seek and variable-sized data in two logical seeks. This ensures fetch and store times are nearly constant with InfiniMem and independent of the number of objects in the file (like random memory access), and enabling:

- Efficient access for Fixed-Sized objects: Using the object ID to index into the datafile, *InfiniMem* gives fast access to fixed-sized objects in 1 logical seek.

- Efficient access for Variable-Sized objects: The metafile enables fast, random-access access to objects in the datafile, in at most 2 logical seeks.

- Random Access Disk I/O: The indexing mechanism provides an imitation of random access to both fixed and variable sized objects on disk.

- Sequential/Batch Disk I/O: To read n consecutive objects, we seek to the start of the first object. We then read sizeof(obj)\*n bytes and up to the end of the last object in the sequence for fixed- and variable-sized objects, respectively.

- Concurrent I/O: For parallel processing, different objects in the datafile must be concurrently and safely accessed. Given the large number of objects, individual locks for each object would be impractical. Instead, *InfiniMem* provides

locks for groups of objects: to decrease lock conflicts, we group non-contiguous objects using modulo ID modulo a MAX\_CONCURRENCY parameter set at 25.

#### 5 Evaluation

We now evaluate the programmability and performance of InfiniMem. This evaluation is based upon three class of applications: probabilistic web analytics, graph/mesh generation, and graph processing. We also study the scalability of size oblivious applications written using InfiniMem with degree of parallelism and input sizes. We programmed size oblivious versions of several applications using InfiniMem and are listed in Table 1. We begin with data analytics benchmarks: frequency counting using arrays, membership query using hash tables, and probabilistic membership query using Bloom filters. Then, in addition to mesh generation, in this evaluation, we use a variety of graph processing algorithms from diverse domains like graph mining, machine learning, etc. The Connected Components (CC) algorithm finds nodes in a graph that are connected to each other by at least one path, with applications in graph theory. Graph Coloring (GC) assigns a color to a vertex such that it is distinct from those of all its neighboring vertices with applications in register allocation etc. In a web graph, PageRank (PR) [14] iteratively ranks a page based on the ranks of pages with inbound links to the page and is used to rank web search results. NumPaths (NP) counts the number of paths between a source and other vertices. From a source node in a graph, Single Source Shortest Path (SSSP) finds the shortest path to all other nodes in the graph with applications in logistics and transportation.

#### 5.1 Programmability

| Application     | Additional LoC | Application      | Additional LoC |  |

|-----------------|----------------|------------------|----------------|--|

| Probabilistic V | Veb Analytics  | Graph Processing |                |  |

| Freq. Counting  |                | Graph Coloring   |                |  |

| Member Query    | 2 + 3 + 3 = 8  | PageRank         |                |  |

| Bloom Filter    | 2 + 4 + 3 = 9  | SSSP             | 1 + 3 + 2 = 6  |  |

| Graph/Mesh      | Generation     | Num Paths        |                |  |

| Mesh Generation | 2+2+2=6        | Conn. Components |                |  |

Table 1: Between 6 and 9 additional lines of code are needed to make these applications size oblivious. Graph processing uses decoupled version (Figure 4b).

Writing size oblivious programs with InfiniMem is simple. The programmer needs to only: (a) initialize the InfiniMem library, (b) identify the large collections and Box or Bag them as necessary, and (c) use the default process()-ing engine or provide a custom engine. Table 1 quantifies the ease of programming with InfiniMem by listing the number of additional lines of code for these tasks to make the program size oblivious using the default processing engine. At most 9 lines of code are needed in this case and InfiniMem does all the heavy lifting with about 700 lines for the I/O subsystem, and about 900 lines for the runtime, all of which hides the complexity of making data structures disk-resident from the user. Even programming the shard processing framework was relatively easy: about 100 lines for simplistic shard generation and another 200 lines for rest of the processing including loading memory and corresponding sliding shards, building the subgraph in memory and processing the subgraph; rest of the complexity of handling the I/O etc., are handled by InfiniMem.

#### 5.2 Performance

We now present the runtime performance of applications programmed with *InfiniMem*. We evaluated *InfiniMem* on a Dell Inspiron machine with 8 cores and 8GB RAM with a commodity 500GB, 7200RPM SATA 3.0 Hitachi HUA722050CLA330

| Input Graph  | V           | E           | Size |

|--------------|-------------|-------------|------|

| Pokec        | 1,632,804   | , ,         |      |

| Live Journal |             | 68,993,773  |      |

| Orkut-2007   |             | 223,534,301 |      |

| Delicious-UI |             | 151,772,443 |      |

| RMAT-536-67  |             | 536,870,912 |      |

| RMAT-805-134 | 134,217,728 | 805,306,368 | 14G  |

Table 2: Inputs used in this evaluation.

hard drive. For consistency, the disk cache is fully flushed before each run.

Size Oblivious *Graph Processing:* We begin with the evaluation of graph processing applications using input graph datasets with varying number of vertices and edges, listed in Table 2. Orkut, Pokec, and LiveJournal graphs are directed graphs representing friend relationships. Vertices in the Amazon graph represent products, while edges represent purchases. The largest input in this evaluation is rmat-805-134 at 14GB on disk, 805M edges and 134M vertices.

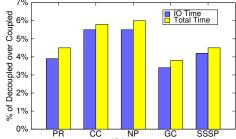

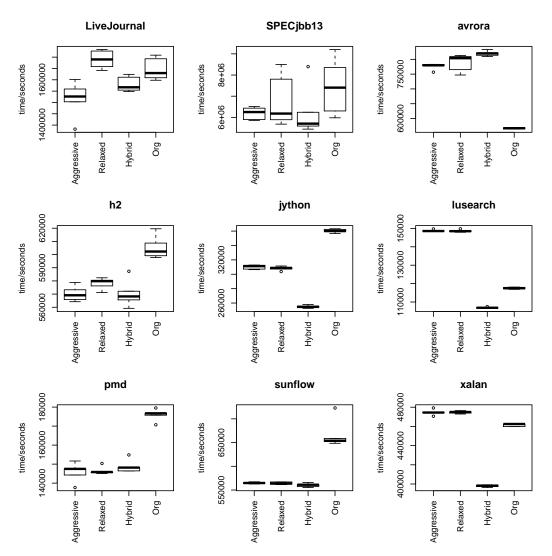

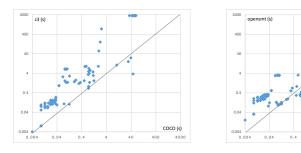

We first discuss the benefits of decoupling edges from vertices. When vertex data and edgelists are in the same data structure, line 22 in Algorithm 1 requires fetching the edgelists for the vertices even though they are not used in this phase of the computation. Decoupling the edgelists from vertex data has the benefit of avoiding wasteful I/O as seen in Table 3. The very large decrease in running time is due to the extremely wasteful I/O that reads the variable sized edgelists along with the vertex data even though

Fig. 7: Percentage(%) of IO and execution time for decoupled over coupled representations for various applications on the 'Delicious-UI' input.

along with the vertex data even though only the vertex data is needed.

Figure 7 shows the I/O breakdowns for various benchmarks on the moderately sized Delicious-UI input. While the programming effort with *InfiniMem* is already minimal, switching between representations for the same program can be easier too: with as little as *a single change* to data structure definition (figures 4a-4b), the programmer can evaluate different representations.

Tables 4 and 5 show the frequencies and percentage of total execution time spent in various I/O operations for processing the *decoupled* graph representation with *InfiniMem*, as illustrated in Figure 4b. Observe that the number of batched vertex reads and writes is the same in Table 4 since both vertices and edgelists are read together in batches. There are no individual vertex writes since *InfiniMem* only writes vertices in batches. Moreover, the number of batched vertex writes is less than the reads since we write only updated vertices and as the algorithm converges, in some batches, there are no updates. Observe in Table 5 that as described earlier, the maximum time is spent in random vertex reads.

| Input Graph  | raph PageRank |       | Conn   | Conn Comp Nump |       | paths | Graph Coloring |       | SSSP  |       |

|--------------|---------------|-------|--------|----------------|-------|-------|----------------|-------|-------|-------|

| Input Graph  | Со            | DeCo  | Со     | DeCo           | Со    | DeCo  | Со             | DeCo  | Со    | DeCo  |

| Pokec        | 2,228         | 172   | 352    | 60             | 37    | 8     | 277            | 28    | 48    | 7     |

| Live Journal | 8,975         | 409   | 1,316  | 122            | 106   | 14    | 602            | 58    | 133   | 70    |

| Orkut        | 3,323         | 81    | 3,750  | 277            | 459   | 11    | 3,046          | 140   | 660   | 154   |

| Delicious-UI | 32,743        | 1,484 | 15,404 | 904            | 1,112 | 67    | 9,524          | 365   | 1,453 | 65    |

| rmat-536-67  | 23,588        | 3,233 | 12,118 | $ 2,\!545 $    | 1,499 | 861   | 5,783          | 1,167 | 1,853 | 584   |

| rmat-805-134 | 25,698        | 3,391 | >8h    | 3,380          | 3,069 | 1,482 | 11,332         | 2,071 | >8h   | 2,882 |

Table 3: Decoupling vertices and edgelists avoids wasteful I/O (runntime time shown is in seconds). 'Co' and 'DeCo' refer to coupled and decoupled respectively.

| I/O Operation           | LiveJournal | Orkut    | Delicious-UI | rmat-536-67 | rmat-805-134 |

|-------------------------|-------------|----------|--------------|-------------|--------------|

| Vertex Batched Reads    | 7,891       | 421      | 40,578       | 12,481      | 24,052       |

| Edge Batched Reads      | 7,891       | 421      | 40,578       | 12,481      | 24,052       |

| Vertex Individual Reads | 865e + 6    | 188e + 6 | 2.8e + 9     | 1.8e + 9    | 2.5e + 9     |

| Vertex Batched Writes   | 7,883       | 413      | 40,570       | 12,473      | 24,044       |

Table 4: Frequencies of operations for various inputs for PageRank.

| I/O Operation           | LiveJournal | Orkut  | Delicious-UI | rmat-536-67 | rmat-805-134 |

|-------------------------|-------------|--------|--------------|-------------|--------------|

| Vertex Batched Reads    | 0.05%       | 0.02%  | 0.31%        | 0.12%       |              |

| Edge Batched Reads      | 8.48%       | 2.75%  | 11.25%       | 7.75%       | 9.72%        |

| Vertex Individual Reads | 54.80%      | 71.59% | 76.96%       | 86.47%      | 81.73%       |

| Vertex Batched Writes   | 0.12%       | 0.03%  | 0.37%        | 0.04%       | 0.10%        |

| Total IO                | 63.45%      | 74.39% | 88.89%       | 94.38%      | 91.68%       |

Table 5: Percentage of time for I/O operations for various inputs for PageRank.

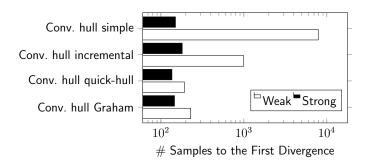

Sharding with InfiniMem: In the rest of this discussion, we always use the decoupled versions of Vertex and EdgeLists. We now compare various versions of graph processing using InfiniMem. Table 6 compares the performance of the two simple graph processing frameworks we built on top of InfiniMem with that of GraphChi-provided implementations in their 8 thread configuration. Infin*iShard* refers to the shard processing framework based on *InfiniMem*. In general, the slowdown observed with InfiniMem is due to the large number of random reads generated, which is O(|E|). For PageRank with Orkut, however, we see speedup for the following reason: as the iterations progress, the set of changed vertices becomes considerably small:  $\sim 50$ . So, the number of random reads generated also goes down considerably, speeding up PageRank on the Orkut input. With Connected Components, our InfiniMem runs slower primarily because the GraphChi converges in less than half as many iterations on most inputs. Table 6 also presents the data for PageRank that processes shards with our InfiniMem library as compared to the very fine-tuned GraphChi library. The speedup observed in Table 6 from InfiniMem to InfiniShard is from eliminating random reads enabled by the shard format. Notice that even with our quick, unoptimized  $\sim 350$  line implementation of sharding, the average slowdown we see is only 18.7% for PageRank and 22.7% for Connected Components compared to the highly tuned and hand-optimized GraphChi implementation. Therefore, we have shown that InfiniMem can be used to easily and quickly provide a size oblivious programming experience along with I/O efficiency for quickly evaluating various representations of the same data.

|              | PageRank Time (sec)  InfiniMem InfiniShard GraphChi (speedup) (speedup) |              |          | Conn. Comp. Time (sec) |                       |          |  |

|--------------|-------------------------------------------------------------------------|--------------|----------|------------------------|-----------------------|----------|--|

| Input Graph  | InfiniMem                                                               | InfiniShard  | CraphChi | InfiniMem              | InfiniShard (speedup) | CraphChi |  |

|              | (speedup)                                                               | (speedup)    | (speedu  |                        | (speedup)             | Graphem  |  |

| Pokec        | 172 (0.72)                                                              | 121 (1.02)   | 124      | 60 (0.40)              | 26 (0.92)             | 24       |  |

| LiveJournal  | 409 (0.90)                                                              | 488 (0.76)   | 371      | 122 (0.49)             | 80 (0.75)             | 60       |  |

| Orkut        | 81 (1.91)                                                               | 190 (0.82)   | 156      | 277 (0.44)             | 142 (0.87)            | 123      |  |

| Delicious-UI | 1,484 (0.43)                                                            | 730 (0.89)   | 652      | 904 (0.17)             | 191 (0.78)            | 149      |  |

| rmat-536-67  | 3,233 (0.36)                                                            | 1,637 (0.70) | 1,146    | 2,545 (0.21)           | 746 (0.71)            | 529      |  |

| rmat-805-134 | 3,391 (0.44)                                                            | 2,162 (0.69) | 1,492    | 3,380 (0.30)           | 1,662 (0.61)          | 1,016    |  |

Table 6: InfiniMem (decoupled) vs. InfiniShard; Speedups over GraphChi.

Size-Oblivious Programming of Probabilistic Apps: Here, we present the throughput numbers for the probabilistic applications in Table 7. We evaluated these applications by generating uniformly random numeric input. Frequency counting is evaluated by counting frequencies of random inserts while membership query and Bloom filter are evaluated using uniformly generated random queries on the previously generated uniformly random input. Jenkins hashes are used in Bloom filter. Bloom filter achieves about half the throughput of Frequency Counting since Bloom filter generates twice as many writes.

We also experimented with querying. We searched for entries using the Orkut input file (3.2GB on disk) as an input file. Using a naive, sequential scan and search took 67 seconds. Using *InfiniMem* with 1

| Application        | Throughput (qps) |

|--------------------|------------------|

| Frequency Counting | 635,031          |

| Membership Query   | 446,536          |

| Bloom Filter       | 369,726          |

Table 7: QPS for the probabilistic apps.

thread took 15 seconds, while using 4 threads took 5 seconds for the *same* naive implementation. The highly optimized GNU Regular Expressions utility took an average of 4.5 seconds for the same search. This shows that in addition to ease of programming, *InfiniMem* performs well even with very simple implementations.

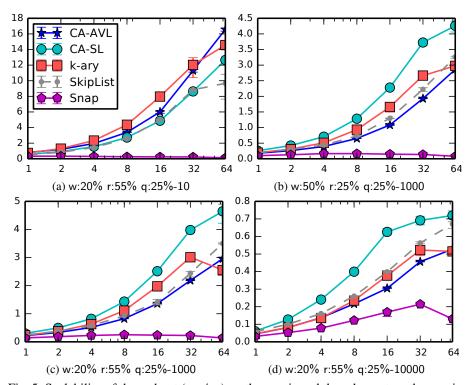

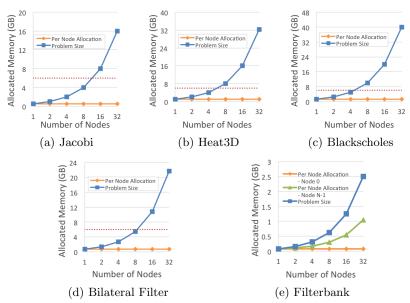

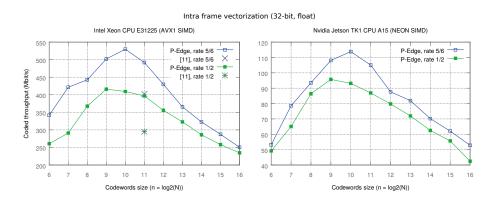

## 5.3 Scalability

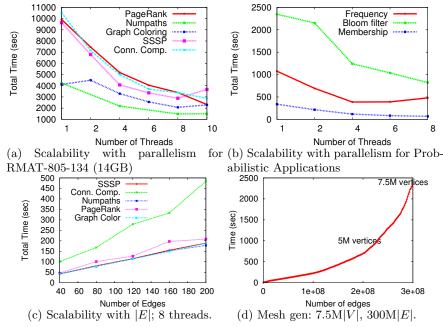

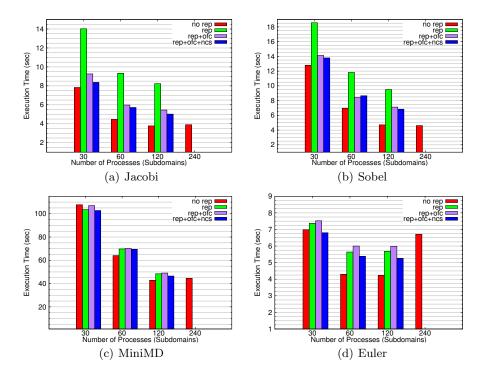

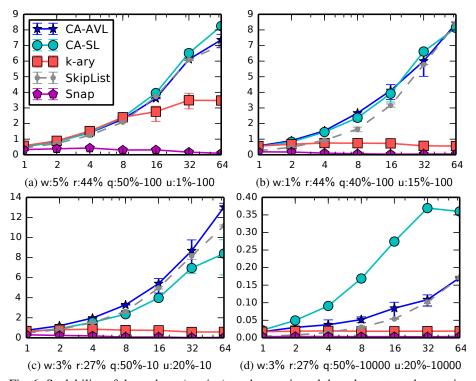

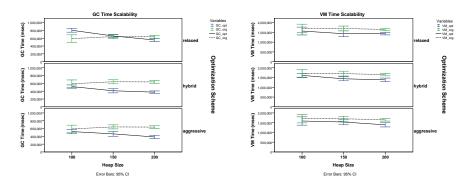

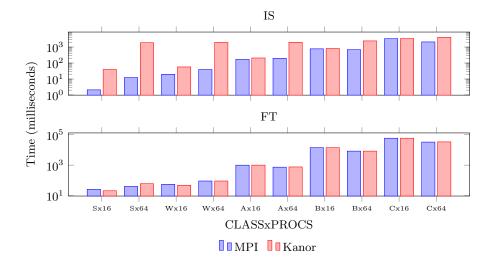

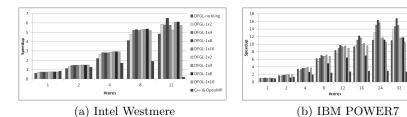

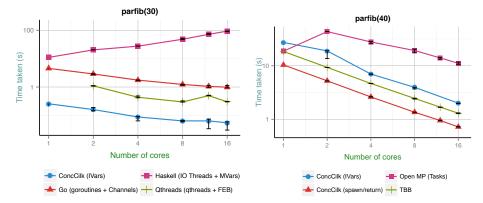

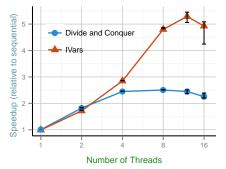

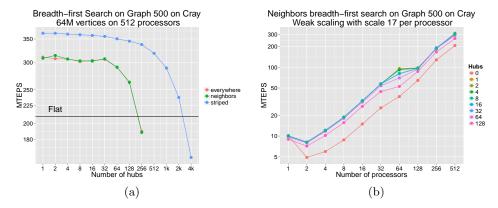

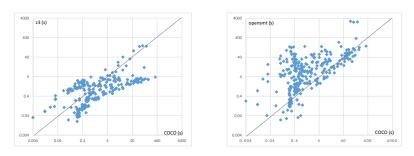

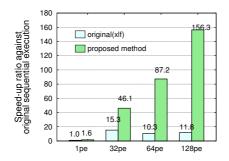

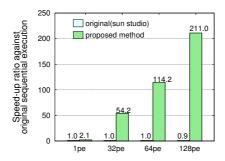

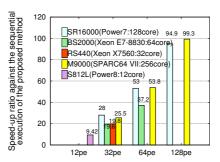

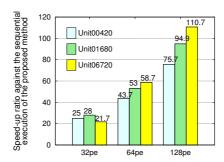

Next, we present data to show that *InfiniMem* scales with increasing parallelism. Figure 8a shows the total running times for various applications on the 14GB rmat-805-134 input: for most applications *InfiniMem* scales well up to 8 threads.

However, given that the performance of applications is determined by the data representation and the number of random accesses that result in disk I/O, we want to study how well *InfiniMem* scales with increasing input size. To objectively study the scalability with increasing number of edges with fixed vertices and controlling for variations in distribution of vertex degrees and other input graph characteristics, we perform a controlled experiment where we resort to synthetic inputs with 4M vertices and 40M, 80M, 120M, 160M and 200M edges. Figure 8c shows the time for each of the for these inputs. We see that with increasing parallelism, *InfiniMem* scales well for increasing number of edges in the graph. This shows that *InfiniMem* effectively manages the limited memory resource by orchestrating seamless offloading to disk as required by the application. The performance on real-world graphs is determined by specific characteristics of the graph like distribution of degrees of the vertices etc. But for a graph of a specified size, Figure 8c can be viewed as a practical upper bound.

Figure 8b illustrates the scalability achievable with programming with *InfiniMem* with parallelism for the Frequency counting, Exact membership query and Probabilistic membership query using Bloom filters. Notice that these applications scale well with increasing number of threads as well as increasing input sizes. The execution time for Bloom filter is significantly larger since Bloom filter generates more random writes, depending on the number of hash functions utilized by the filter; our implementation uses two independent hashes.

Fig. 8: Scalability of *InfiniMem* with parallelism and input size.

Figure 8d illustrates that very large graph generation is feasible with *Infinimem* by showing the generation of a Mesh with 7.5M vertices and 300M edges which takes about 40 minutes (2400 seconds). We observe that up to 5M vertices and 200M edges, the time for generation increases nearly linearly with the number of edges generated after which the generation begins to slow down. This slowdown is not due to the inherent complexity of generating larger graphs: the number of type of disk operations needed to add edges is independent of the size of the graph – edge addition entails adding the vertex as the neighbor's neighbor and accessing the desired data in *InfiniMem* requires a maximum of 2 logical seeks. The reason for the observed slowdown is as follows: modifications of variable sized data structures in *InfiniMem* are appended to the datafile on disk; this data file, therefore, grows very large over time and the disk caching mechanisms begin to get less effective. Compare this with the fact that GTGraph crashed immediately for a graph with just 1M vertices and 400M edges.

# 5.4 Integration with Distributed Shared Memory (DSM)

Next we demonstrate the applicability of Size Oblivious Programming in the context of Distributed Shared Memory. While clusters are easy to *scale out*,

multi-tenant environments can restrict memory available to user processes or certain inputs may not fit in the distributed memory. In either case, it would be beneficial to have the programs run successfully without rewrites. We applied

the *InfiniMem* framework to seamlessly make our object based DSM [9] size oblivious. When the data allocated to the node does not fit in available memory, the DSM system spills data to local disk and fetches it back to local memory as demanded by the application. When running distributed software speculation with 75% of the input in memory and the rest spilt to disk, *InfiniMem* has much lower overhead as compared to an al-

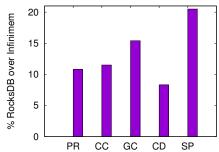

Fig. 9: Extra overhead of RocksDB over *InfiniMem* in our DSM.

ternative solution based upon RocksDB [7]: Figure 9 shows that RocksDB based programs run up to  $\sim 20.5\%$  slower than using InfiniMem. Compared to when all the data fits in memory, InfiniMem introduces a small overhead of 5% over our baseline DSM, i.e. at this small cost, InfiniMem makes our DSM size oblivious.

# 6 Related Work

The closest file organization to that used by *InfiniMem* and illustrated in Figure 6 is the B+ tree representation used in database systems. The primary differences in our design are the following: (1) *InfiniMem* uses a flat organization, with at most one level index for variable sized data. (2) *InfiniMem* provides O(1) time I/O operations for random access while the B+ trees require O(log n) time.

Out-of-core Computations—In this paper, we enable applications with very large input data sets to efficiently run on a single multicore machine, with minimal programming effort. The design of the InfiniMem transparently enables large datasets become disk-resident while common out-of-core algorithms [5,10,20] explicitly do this. As demonstrated with shards, it should be easy to program these techniques with InfiniMem.

Processing on a Single Machine—Traditional approaches to large-scale data processing on a single machine involve using machines with very large amounts of memory, while *InfiniMem* does not have that limitation. Examples include Ligra [16], Galois [15], BGL [18], MTGL [3], Spark [21] etc. FlashGraph [6] is a semi-external memory graph processing framework and requires enough memory to hold all the edgelists; *InfiniMem* has no such memory requirements.

GraphChi [11] recently proposed the Parallel Sliding Window model based on *sharded* inputs. Shard format enables a complete subgraph to be loaded in memory, thus avoiding random accesses. GraphChi is designed for and works very well with algorithms that depend on static scheduling. *InfiniMem* is general-purpose and recognizes the need for sequential/batched *and* random input for fixed *and* variable sized data and provides simple APIs for rapid prototyping.

#### 7 Conclusion

We have presented the *InfiniMem* system for enabling size oblivious programming. The techniques developed in this paper are incorporated in the versatile

general purpose InfiniMem library. In addition to various general purpose programs, we also built two more graph processing frameworks on top of InfiniMem: (1) with a simple data format and (2) to process GraphChi-style shards. We have shown that InfiniMem performance scales well with parallelism, increasing input size and highlight the necessity of concurrent I/O design in a parallel set up. Our experiments show that InfiniMem can successfully generate a graph with 7.5 million vertices and 300 million edges (4.5 GB on disk) in 40 minutes and it performs the PageRank computation on an RMAT graph with 134M vertices and 805M edges (14GB on disk) an 8-core machine in about 54 minutes.

#### References

- 1. Avery, C.: Giraph: large-scale graph processing infrastruction on hadoop. Proceedings of Hadoop Summit. Santa Clara, USA:[sn] (2011)

- Bader, D.A., Madduri, K.: Gtgraph: A synthetic graph generator suite. Atlanta, GA, February (2006)

- 3. Berry, J., Mackey, G.: The multithreaded graph library (2014)

- 4. Bu, Y., Borkar, V., Xu, G., Carey, M.J.: A bloat-aware design for big data applications. In: Proc. of ISMM 2013. pp. 119–130. ACM (2013)

- Chiang, Y.J., Goodrich, M.T., Grove, E.F., Tamassia, R., Vengroff, D.E., Vitter, J.S.: External-memory graph algorithms. In: Proc. of SODA '95. pp. 139–149

- 6. Da Zheng, D.M., Burns, R., Vogelstein, J., Priebe, C.E., Szalay, A.S.: Flashgraph: processing billion-node graphs on an array of commodity ssds

- 7. Facebook: RocksDB Project, RocksDB.org

- 8. Gonzalez, J.E., Low, Y., Gu, H., Bickson, D., Guestrin, C.: Powergraph: Distributed graph-parallel computation on natural graphs. In: OSDI '12. pp. 17–30

- 9. Koduru, S-C., Vora, K., Gupta, R.: Optimizing Caching DSM for Distributed Software Speculation. In: Proc. Cluster 2015.

- 10. Kundeti, V.K., et al.: Efficient parallel and out of core algorithms for constructing large bi-directed de bruijn graphs. BMC bioinformatics 11(1), 560 (2010)

- 11. Kyrola, A., Blelloch, G., Guestrin, C.: Graphchi: Large-scale graph computation on just a pc. In: Proc. of the 10th USENIX Symposium on OSDI. pp. 31–46 (2012)

- 12. Low, Y., Gonzalez, J., Kyrola, A., Bickson, D., Guestrin, C., Hellerstein, J.M.: Graphlab: A new framework for parallel machine learning. arXiv:1006.4990 (2010)

- 13. Malewicz, G., et al.: Pregel: a system for large-scale graph processing. In: Proc. of the 2010 ACM SIGMOD ICMD. pp. 135–146. ACM (2010)

- 14. Page, L., Brin, S., Motwani, R., Winograd, T.: The pagerank citation ranking: Bringing order to the web. (1999)

- Pingali, K., Nguyen, D., Kulkarni, M., Burtscher, M., Hassaan, M.A., Kaleem, R., Lee, T.H., Lenharth, A., Manevich, R., Méndez-Lojo, M., et al.: The tao of parallelism in algorithms. In: ACM SIGPLAN Notices. vol. 46, pp. 12–25 (2011)

- 16. Shun, J., Blelloch, G.E.: Ligra: a lightweight graph processing framework for shared memory. In: Proc. PPoPP 2013. pp. 135–146. ACM (2013)

- 17. Shvachko, K., Kuang, H., Radia, S., Chansler, R.: The hadoop distributed file system. In: IEEE MSST, 2010. pp. 1–10 (2010)

- 18. Siek, J., Lee, L., Lumsdaine, A.: The boost graph library (bgl) (2000)

- 19. Team, T., et al.: Apache mahout project (2014), https://mahout.apace.org

- Toledo, S.: A survey of out-of-core algorithms in numerical linear algebra. External Memory Algorithms and Visualization 50, 161–179 (1999)

- 21. Zaharia, M., Chowdhury, M., Franklin, M.J., Shenker, S., Stoica, I.: Spark: cluster computing with working sets. In: Proc. HotCloud 2010. pp. 10–10 (2010)

# Low-Overhead Fault-Tolerance Support using DISC Programming Model

Mehmet Can Kurt<sup>1</sup>, Bin Ren<sup>2</sup> and Gagan Agrawal<sup>1</sup>

Department of Computer Science and Engineering, The Ohio State University, Columbus OH, USA

kurt@cse.ohio-state.edu, agrawal@cse.ohio-state.edu

Pacific Northwest National Laboratory, Richland WA, USA

bin.ren@pnnl.gov

Abstract. DISC is a newly proposed parallel programming paradigm that models many classes of iterative scientific applications through specification of a domain and interactions among domain elements. Accompanied with an associated runtime, it hides the details of inter-process communication and work partitioning (including partitioning in the presence of heterogeneous processing elements) from the programmers. In this paper, we show how these abstractions, particularly the concepts of compute-function and computation-space objects, can be also used to leverage low-overhead fault-tolerance support. While computation-space objects enable automated application level checkpointing, replicated execution of compute-functions helps detect soft errors with low overheads. Experimental results show the effectiveness of the proposed solutions.

# 1 Introduction

High performance computing is undergoing a significant transformation in the sense that resilience is becoming as equally important as performance. Computing power is constantly being increased with more number of cores, hence with more parallelism. This trend results in a significant decrease in Mean Time To Failure (MTTF) rates in HPC systems due to the large number of components. At the same time, parallel machines are becoming more memory and I/O bound. These two trends together are implying that resilience is not only a major problem, but also the commonly used solutions for fault-tolerance, mostly based on system-level checkpointing, are becoming too expensive. The total cost of fault-tolerance support with checkpointing, which is the sum of the costs of taking checkpoints (which increases as checkpointing frequency increases), the net time spent on recomputation (which increases as checkpointing frequency decreases), and the time spent on restart after a failure, can dominate the actual execution time. An analysis of a 100,000 core job, where each node has a MTTF of 5 years, indicates that these three costs can add up to 65% of the total execution time, i.e. only 35% of the time will be productively used [10]. Technology trends indicate that this situation will only get worse in the near future in the sense that MTTF values will become so small that the time required to complete a checkpoint can exceed the MTTF making the existing approach completely inapplicable [4].

Moreover, in recent years, there is a growing concern about a new class of failures, namely, soft errors. These errors involve bit flips in either processing cores,

the memory, or the disk. Although radiation has been considered the main cause of such random bit flips [20], use of smaller and smaller transistors and efforts to improve power-efficiency in hardware are now attributed as the cause of these faults occurring more frequently [25]. Many recent publications have summarized the observed frequency of these faults [10], for example, double bit flips (which cannot be corrected by Error Correcting Codes) occur daily at a national lab's Cray XT5, and similary, such errors were frequent in BG/L's unprotected L1 cache. Although the traditional solutions to deal with soft errors have been implemented at the hardware level, clearly there is a need for software solutions to this problem.

These developments are imposing new challenges for application programmers. On one hand, they need to be able to manually implement efficient application-level checkpointing and recovery. Even more challenging for them is to implement techniques for dealing with soft errors. One pressing question is whether programming models can help automate fault-tolerant solutions.

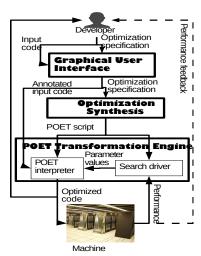

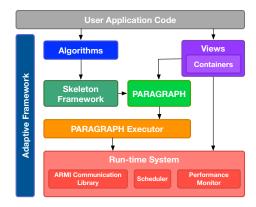

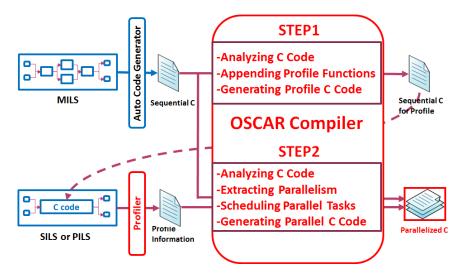

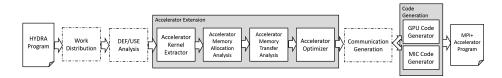

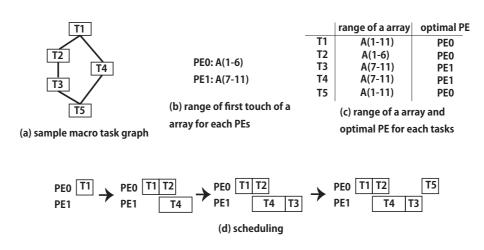

In this paper, we address this question in the context of the DISC programming model recently developed by the authors. DISC [15] is a programming model and associated runtime system based on domain and domain element interaction concepts and particularly targets iterative scientific applications with structured grids, unstructured grids and N-body simulation patterns. While these applications have different communication patterns, they are similar in an important way, i.e, they have an underlying domain, and most of the computation occurs due to the interactions among domain elements. Our programming model supports an API by which the domain, interaction among domain elements, and functions for updating any attributes of these domain elements can be explicitly specified. Starting from this model, inter-process partitioning of the work and the communication is handled automatically by the runtime system. Our previous work has shown how the system is almost as efficient as MPI for homogeneous clusters, while allowing repartitioning of work for dealing with heterogenous configurations.

In this paper, we examine another important application of this programming model. We extended DISC model so that it also leverages low-overhead fault-tolerance support. We show that the abstractions that DISC model provides to hide the details of process communication and work partitioning/re-partitioning help also identify the main execution state and the functions that are the most susceptible to soft errors. Exposure of such vital program state and instructions is utilized in order to implement two fault-tolerance mechanisms within the runtime. First, with the concept of computation-space objects, DISC API makes it feasible to support automated, yet efficient, application-level checkpointing. This as a result can reduce checkpointing overheads significantly. Second, with the concept of compute-functions, DISC runtime is capable of detecting soft errors using a partial replication strategy. Here, only the set of instructions most likely to corrupt the main execution state is executed with redundancy and the results are compared efficiently with computed checksums.

To show the effectiveness of our approach, we have developed two stencil computations, one unstructured grid based computation, and a molecular dynamics miniapplication (MiniMD, a representative of a full-scale molecular dynamics application). We first compare the cost of checkpointing in our model, against system-level checkpointing in MPI (which is the only automated solution available today). Next, we compare the performance of DISC implementations with replication support to

normal execution without any redundancy and show how further improvements in replication overheads can be achieved.

#### 2 Related Work

Fault-tolerance for high performance computing against hard errors has been extensively studied. Much of this research specifically targets MPI [26, 14, 1, 6, 3, 12, 17]. Recent efforts on optimizing the process include combination of coordinated and uncoordinated checkpointing [23] and compression for reducing the overheads of checkpointing [13]. Another approach is algorithm-level fault-tolerance [19, 2, 5, 7]. where properties of an algorithm are exploited (typically to build-in redundancy). While this approach can overcome many of the overheads of general checkpointing, it has two key limitations: 1) as the name suggests, the solution is very specific to a particular algorithm, and 2) the fault-tolerant algorithm needs to be implemented by the programmer manually while developing the application. As for soft errors, the general detection approach is through redundant execution. This redundancy can be achieved at various levels. For instance, in [18], each computing node in execution is paired with a buddy node that performs the same work. Paired nodes checkpoint and exchange their local state periodically and the resulting computations in paired nodes are cross compared through their respective checkpoints. [10] provides a new MPI implementation that creates replica MPI tasks and performs online verification during communication only on MPI messages. Studies in [22, 24 execute all dynamic instructions in a program twice by redundant threads and compare the first and second result. If there is a mismatch, both threads restart execution from the faulty instruction. There have been some efforts to reduce the overheads associated with redundancy; [27] exploits high-level program information at compile time to minimize data communication between redundant threads, whereas [21] explores the partial redundant threading spectrum, in which only a dynamic subset of instructions is duplicated to near single threaded execution performance at the expense of limited fault coverage. [9] combines redundant threading with symptom-based detectors by quantifying the likelihood that a soft-error impacting an instruction creates a symptom such as branch mispredicts or cache misses. Resultingly, it only duplicates the instructions that can not generate any such symptoms. Although the proposed solutions achieve significant reductions in associated overheads, none of them attempts to implement redundancy at the programming model level. As we show in next sections, proper abstractions at programming model level can expose the most vital program state and instructions and can help automate redundant execution with small overheads.

# 3 DISC Programming Model

In this section, we present the key concepts of DISC programming model as a background for next section which explains how its abstractions leverage low-overhead fault-tolerance support.

#### 3.1 Domain and Subdomain

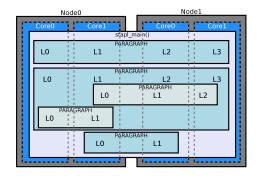

DISC model treats the entire input space of an application as a multidimensional domain, which consists of domain elements. At the beginning of execution, programmers provide information about the domain. This information is used to initialize the runtime system and it includes 1) whether the domain represents a

structured grid, an unstructured grid or a particle set, 2) number of dimensions and boundary values for each dimension and 3) the type of interaction among domain elements. Once this information is passed to the runtime, it decomposes the entire domain into non-overlapping rectilinear regions referred as *subdomains* and assigns each subdomain to a processing unit. Since subdomain decomposition and assignment is performed by the runtime, it is able to hold a high-level view of the domain.

As a concrete example, consider a molecular dynamics application such as MiniMD which simulates the motion of a large number of atoms in three-dimensional space throughout a predefined number of time-steps. When implemented using DISC model, the three-dimensional space is treated as an N-body simulation domain and each atom in the simulation corresponds to a domain element. DISC runtime for MiniMD is initialized with the following lines of code;

```

// provide domain information and initialize DISC runtime DomainProps props; props.set_ndims(3); // number of dimensions props.set_min_bounds(0, 0, 0); // x, y, z min_bounds props.set_max_bounds(XMAX, YMAX, ZMAX); // x, y, z max_bounds NBodyDomain domain(props);

```

#### 3.2 Attributes

Each domain element in a DISC domain has associated coordinate values. In some domain types such as structured grids, coordinate values of domain elements might stay fixed during the entire execution and can be inferred directly from the boundary values of assigned subdomains. However, for other domain types, they might be updated periodically and their initial values should be explicitly provided by programmers. In addition to coordinates, each domain element can also be associated with a set of attributes. For instance, each atom in MiniMD has three additional attributes that store velocity values of the corresponding atom on x, y and z axis. The key advantage of DISC model is its ability to perform data exchange operations based on the interaction pattern automatically and to re-partition the domain on the fly in presence of heterogeneity by migrating domain elements within the domain. To fulfill both of these promises, programmers register coordinates and attributes of domain elements within each subdomain via DISC API, so that the runtime is informed of the data structures that maintain associated information on each domain element. Using the same example, the code snippet below shows how attributes of domain elements in MiniMD are passed to the runtime through DISC objects called *DoubleAttribute*;

```

DoubleAttribute velocities[3]; // x, y, z velocities

/* fill in attribute object velocities with initial values of x, y, z velocities */ domain.register_attributes(&velocities);

```

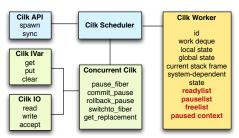

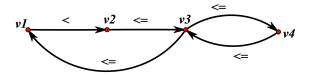

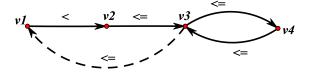

#### 3.3 Compute-Function and Computation-Space

In DISC model, each processing unit performs computations for the assigned portion of the domain. In other words, the domain elements that a processing unit processes lie within the boundaries of the subdomain that has been assigned to it by the runtime. DISC requires programmers to express underlying computation, which typically comprises of calculating new values for attributes associated with domain elements, in a single or a set of functions referred as *compute-functions*. Compute-functions generally host the portion of code on which most of the execution time is spent. Programmers specify these functions by passing function pointers to the runtime. At each iteration during a program's execution, the runtime invokes these functions in the order that they are specified.

For each compute-function, programmers explicitly declare one or more objects called *computation-space*. A computation-space object coupled with a compute-function stores the results of computation carried out by that function. It generally contains an entry for each domain element in the corresponding subdomain and programmers perform any updates related to the domain elements directly on the computation-space object itself. This way, the runtime is aware of what additional data structures along with coordinates and attributes describe the domain elements in a subdomain completely. This abstraction leverages automated migration of domain elements within the domain if needed. Note that mapping a value in computation-space to the corresponding domain element can be inferred from domain type in most cases. Otherwise, programmers can pass additional functions to the runtime that dictate this mapping.

In MiniMD, atoms interact with other atoms in a given radius and this interaction results in recomputation of coordinates and velocities of each atom at every time-step. The code snippet below reflects this by defining six computation-space objects (three for new coordinates and three for new velocities). These objects are coupled with the compute-function *minimd\_kernel* and passed to the runtime via DISC API;

DoubleAttribute computation\_space[6]; // new x, y, z coords and velocities domain.add\_compute\_function(minimd\_kernel, &computation\_space);

#### 3.4 Interaction between domain elements

As indicated before, a key advantage of DISC model is that the runtime handles communication automatically based on the type of interaction between domain elements. Currently, DISC model supports three types of communication; based on nearest neighbor interactions in stencil kernels, based on radius-based interactions in molecular dynamics applications and based on a list provided explicitly by programmers that dictates pair-wise interactions. Further details for runtime communication generation can be found in [15].

# 4 Fault-Tolerance Support

We now describe two fault-tolerance approaches that have been implemented for the applications developed using DISC model.

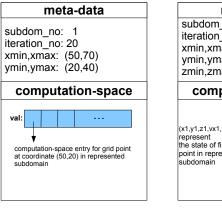

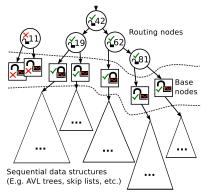

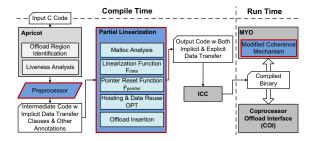

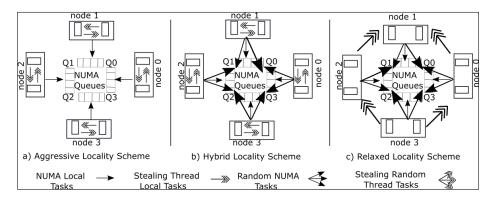

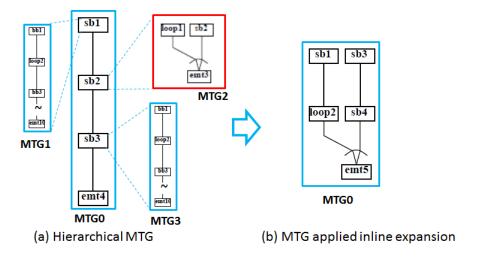

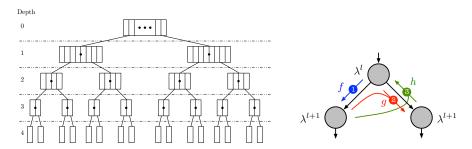

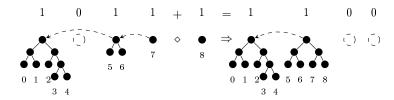

(a) Structured Grid

(b) Particle Set

**Fig. 1.** Sample checkpoint files for a 2D stencil (a) and 3D molecular dynamics application (b). Both files consist of two parts as meta-data and computation-space objects.

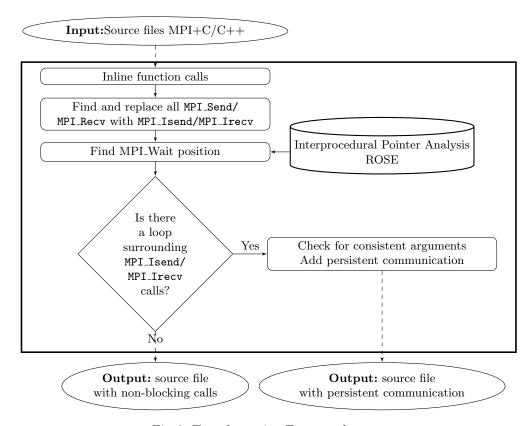

#### 4.1 Checkpointing

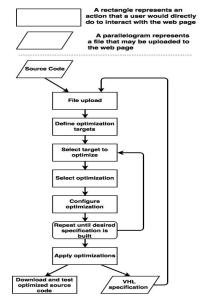

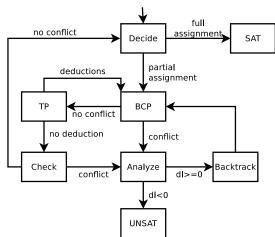

DISC model automates application-level checkpointing, alleviating the need for expensive system-level checkpointing that is normally used for programming models like MPI. Like any checkpointing-based approach, we assume the existence of a persistent storage where the checkpoint files can be written into.

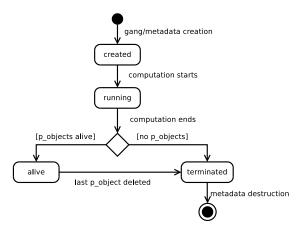

Two important questions for application-level checkpointing are: 1) when should checkpoints be taken, and 2) what data structures will be needed to restart the computation in case of a failure, and therefore, need to be checkpointed. It turns out that the DISC model simplifies these decisions. Particularly, the end of an iteration of the time-step loop (after data exchange and main computation have been completed by the runtime system) is a natural point for taking the checkpoint. Compared to system-level checkpointing, we get a coordinated checkpoint (in the sense that there is no need for message logging for recovery), while not requiring any time-consuming coordination between processes.

Now, let us return to the question of which data structures need to be check-pointed. DISC model encapsulates the computational progress made on each domain element in objects that we introduced in previous section; attribute and computation-space objects. At each iteration, attribute objects store the current information associated with domain elements, whereas computation-space objects capture the updates on them performed through compute-functions. As a concrete example, if we consider MiniMD, after each time-step, the attributes and the computation-space objects contain previous and updated coordinate and velocity values of each atom. The collection of attribute and computation-space objects represent the main execution state of applications at any given time. This collection along with the high-level information such as initial domain decomposition (boundaries of each subdomain) can be used to recover the state of DISC runtime and the underlying application completely.

If an application has multiple compute-functions, not all computation-space objects may be live at the end of an iteration of the time-step loop, i.e. certain computation-space objects could have been consumed already. Moreover, some of the attribute objects might entirely depend on and be calculated from a small set of remaining attributes without incurring a significant recomputation cost. This implies that during failure recovery not all of the attributes and computation-space objects are needed to recreate the execution state of domain elements. Some of them can be ignored by the checkpointing mechanism to save bandwidth, hence time, and also storage space. While compiler analysis can provide this information, our model currently asks the programmers to explicitly annotate this information by passing additional arguments during instantiation of these objects. This way, programmers can explore the tradeoff space in checkpointing the entire domain state vs. recalculation of a small portion from saved data structures. Note that any other application state besides the ones associated directly with domain elements should be explicitly checkpointed by programmers. However, considering the computation patterns that DISC model targets, such additional state is limited and recomputed efficiently from checkpointed attribute and computation-space objects.

Checkpointing frequency as well as other important information like the file path where the checkpoint files will reside can be set via DISC API. We insert some meta-data information to the head of checkpoint files including the current iteration number, and also the boundaries of the subdomain that attribute and computation-space objects represent. This meta-data is utilized to reconstruct the application state during recovery. Figures 1(a) and (b) illustrate the content of sample checkpoint files, which are taken at the  $20^{th}$  iteration of a 2D stencil grid computation and a 3D molecular dynamics application. In both (a) and (b), only the computation-space objects are saved.

**Recovery** During recovery from a failure, DISC model is able to restart the computation both with the same or a fewer number of processes, unlike the current checkpointing approaches in MPI, which can only allow restart with the same number of processes. For instance, assuming that there are N processing units in the system before the failure, if the computation is restarted with a fewer number of nodes, say N-1, the domain is decomposed into N-1 subdomains.

Whether with the same or fewer number of nodes, the most critical operation for recovery is to recreate the computational state of a subdomain from existing checkpoint files. If a processing unit has been assigned the same subdomain as before, it will be sufficient to access that subdomain's checkpoint file and load its content into computation-space object in entirety. However, after decomposition, a change in subdomain boundaries is very likely. Therefore, each processing unit may need to read several checkpoint files. In such cases, the metadata information mentioned previously is utilized to filter down the checkpoint files either completely or at least partially, i.e. we check if there is an intersection between processing unit's newly assigned subdomain and the boundaries of the subdomain that the checkpointed computation-space object represents.

Once computation-space objects for the new domain have been reconstructed from the checkpoint files, application can restart from the iteration in which the last checkpoint was taken.

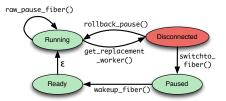

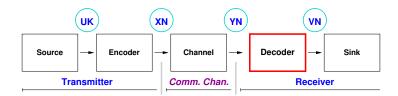

Fig. 2. Flow of execution at each iteration when replication strategy is in use.

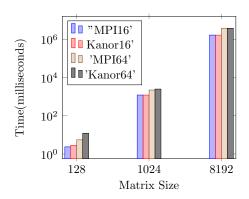

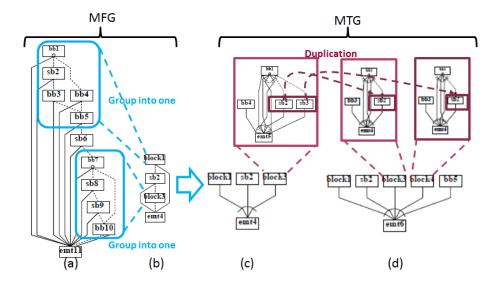

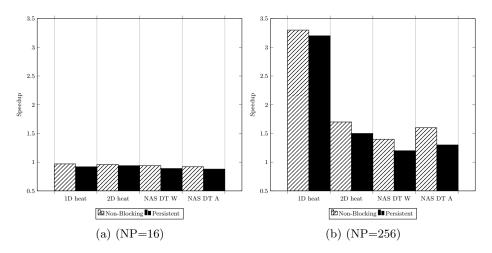

#### 4.2 Replication

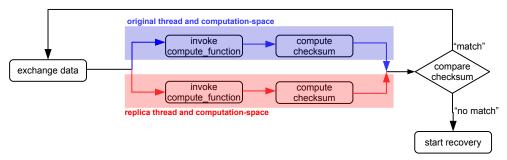

Soft error detection has drawn significant attention from community in recent years. Such error detection could be from a variety of sources including hardware or software error detection codes such as ECC, symptom-based error detectors [11] and application-level assertions. One approach to detect such errors is to create two or more independent threads of execution and compare the execution state of different threads. This work has been done at multiple levels – replication at process level [10] or replication at the instruction level [9]. However, trivial replication of the entire program execution and comparison of resulting computation might incur significant overheads. We claim that concepts of *compute-functions* and *computation-space* objects in DISC model can be used to implement a partial replication strategy to reduce associated overheads substantially.

As emphasized before, compute-functions contain the lines of code to which majority of program execution time is devoted. A soft error in combinatorial logic components including register values, ALUs and pipeline latches is most likely to occur when processing cores carry out the instructions expressed in computefunctions. Since computations, and hence updates on domain elements, defined in compute-functions are directly reflected on the computation-space objects coupled with them, a soft error occurring during the execution of these functions eventually corrupts the computation-space objects, either directly and transitively. This observation suggests that soft errors can be efficiently detected by replication of compute-functions only and cross-comparison of their associated computationspace objects after each iteration. Note that replication mechanism described next assumes that processor components other than the memory are susceptible to soft errors. A produced value is assumed to be resilient once it leaves the processor and is stored back in memory. Control flow variables and memory references are protected by other means such as invariant assertions against the possibility of causing fatal errors such as segmentation faults. Hence, we mainly protect execution against soft errors on calculated values that are used to update computation-space objects.

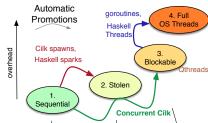

**Replication mechanism** Figure 2 demonstrates the execution flow at each iteration when this partial replication strategy is implemented in the DISC runtime. After data exchange operations are performed, the runtime splits the main execution thread into two as *original* and *replica*. Each thread is associated with its

own computation-space object, but they both invoke the same compute-function in parallel. During compute-function execution, both original and replica threads use the same set of input space, i.e. attributes of domain elements and any global data structures in application code. Sharing the same memory space, except the computation-space objects, leads to a significant reduction in overall memory footprint of replication strategy.

Currently, the replication strategy in DISC model makes the assumption that compute-functions provided by the programmer are side-effect free, meaning that they do not modify any global data structures. This is mainly to avoid possible race conditions. Note that one can synchronize original and replica threads by pragma directives with respect to the threading library used by the DISC runtime.

Checksum calculation After both threads finish executing the compute-function, they calculate a checksum value over their own computation-space object. We employ integer module operation as the checksum function. Regardless of their data type, we treat the bit representation of values in computation-space objects as an integer and accumulate them into a single sum [16]. After checksum calculation, the two threads merge and checksum values are compared by the main thread. If the values match, application advances to the next iteration. Otherwise, DISC runtime ceases the execution and informs the programmer that a soft error has been detected and a recovery procedure should be initiated.

Improvements for cache utilization The initial replication scheme calculates checksums over computation-space objects once individual threads finish execution of compute-functions. Although checksum calculation can be performed quite efficiently, especially in architectures with vector units, accessing the entire computation-space objects once again leads to a large number of cache misses, and hence to high overheads, especially when computation-space objects are large. To remedy this, we present an improvement on top of the plain replication scheme presented previously. Instead of performing it in a separate step, we incorporate checksum calculation directly into compute-functions. Particularly, pure compute-functions provided by programmers are modified in a way that entries in a computation-space object contribute to the checksum on the fly, right after they are assigned a value. On the fly checksum calculation increases temporal locality of overall replication strategy and helps us avoid the data access costs incurred by an isolated checksum calculation phase.

Another source of overhead is the need to create a second copy of computation-space objects. Having additional computation-space objects for replica threads both increases the total memory footprint and at the same time diminishes overall cache utilization. Thus, as a second improvement, we avoid creating replica computation-space objects by modifying compute-functions further. Particularly, assignments to computation-space objects in replica thread are replaced by instructions that accumulate the assigned variables to the checksum values instead. Having no replica computation-space object in replica threads results in further improvements in data locality. In the next section, we demonstrate how these two optimizations affect performance of replication strategy, especially for applications with large output space.

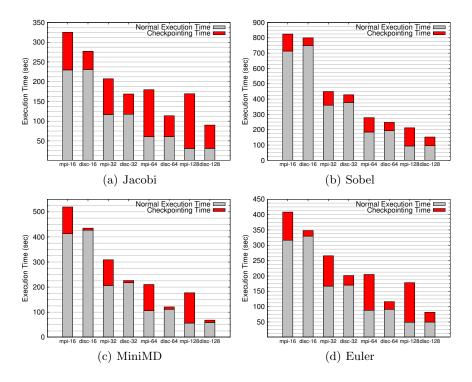

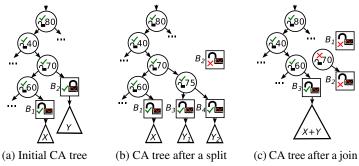

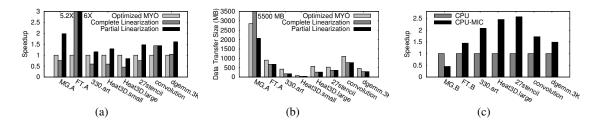

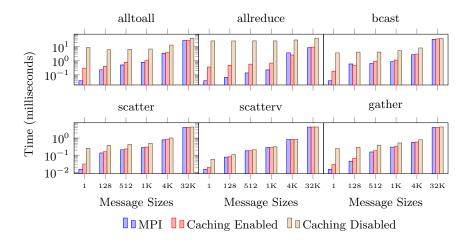

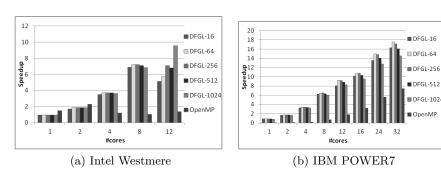

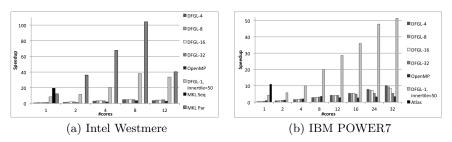

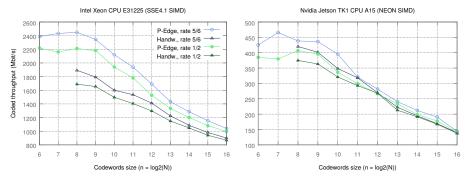

Fig. 3. Normal execution and checkpointing times of MPI and DISC implementations of four applications with varying number of nodes.

## 5 Experiments

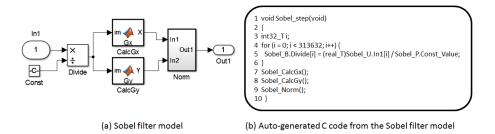

In this section, we present results from a number of experiments we conducted to evaluate the fault-tolerance solutions that we implemented within DISC model. Our evaluation is based on four applications. We chose one molecular dynamics application (MiniMD), one application involving an unstructured grid (Euler), and two smaller kernels involving stencil computations (Jacobi and Sobel).

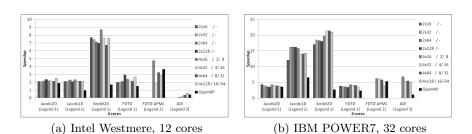

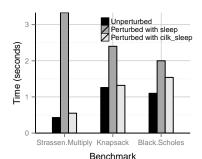

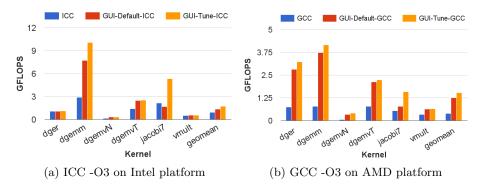

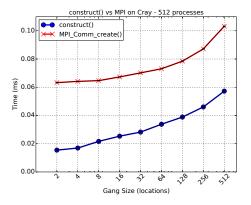

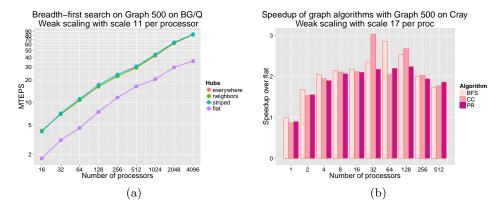

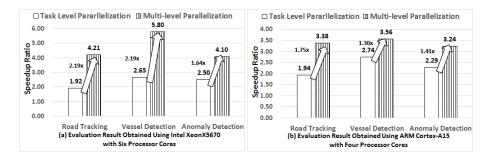

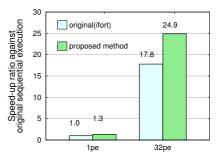

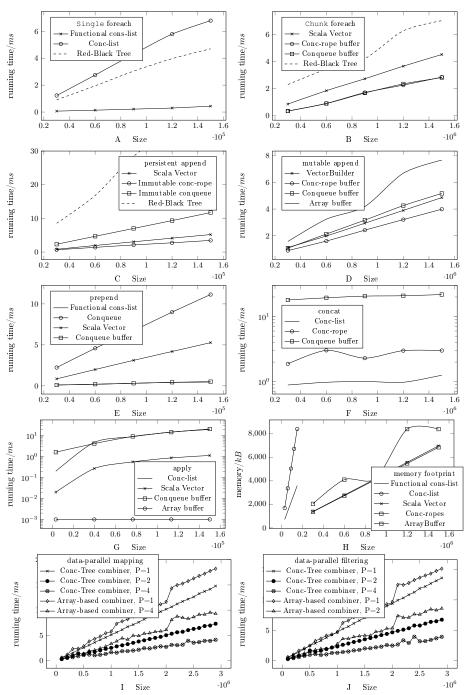

#### 5.1 Checkpointing

One of the key advantages of DISC model is the support for automated applicationlevel checkpointing. We now show how the cost of checkpointing with our approach compares with the only automated solution currently available with MPI, which is system-level checkpointing. Moreover, we also examine how the total execution time of our system and MPI versions compare, when checkpointing overheads are included.

For checkpointing support in MPI implementations, we used MPICH2-BLCR, which is one of the most popular system-level checkpoint/restart libraries. MPI versions of all evaluated applications have been written by ourselves, except Min-iMD which was obtained from the Mantevo suite<sup>3</sup>. Experiments in this section are performed on a cluster where each node has two quad-core 2.53 GHz Intel(R) Xeon(R) processors, with 12 GB RAM, executing RedHat Enterprise Linux Server

<sup>&</sup>lt;sup>3</sup> Please see https://software.sandia.gov/mantevo

release 6.1, and Gigabit ethernet as the interconnect. Our programming model is implemented in C++ language and uses MPICH2 (version 1.4.1p1) as the underlying communication library. The comparisons have been performed over a varying number of nodes ranging between 16 and 128 (with only one core at each node), consistent with our focus on distributed memory parallelism. Both in this and next section, we repeated each experiment 5 times and report the average results.